24小時(shí)聯(lián)系電話:18217114652、13661815404

中文

行業(yè)資訊

高速PCB設(shè)計(jì)中的走線長(zhǎng)度匹配

每個(gè)電子信號(hào)都需要一定的時(shí)間才能沿著導(dǎo)體傳播并到達(dá)目的地。由于電路板上的分散和損耗,在某些情況下需要對(duì)高速電路板上的PCB走線長(zhǎng)度進(jìn)行匹配。當(dāng)您知道如何識(shí)別需要長(zhǎng)度匹配的電路板部分時(shí),可以采取重要步驟來(lái)確保信號(hào)按時(shí)到達(dá)接收器。

如果信號(hào)速度和任何跡線長(zhǎng)度不匹配之間的聯(lián)系不明顯,則可以將允許的跡線不匹配確定為時(shí)間差(對(duì)于數(shù)字信號(hào))或相位差(對(duì)于模擬信號(hào))。PCB走線長(zhǎng)度匹配通常以差分對(duì)的形式進(jìn)行討論,但也適用于具有單端信號(hào)的網(wǎng)絡(luò)和總線以及差分驅(qū)動(dòng)的總線。由于計(jì)算機(jī)外圍設(shè)備和其他數(shù)字系統(tǒng)需要連續(xù)更快的運(yùn)行速度,因此計(jì)算機(jī)網(wǎng)絡(luò)中的傳播延遲在承載數(shù)字信號(hào)的導(dǎo)體中允許的走線長(zhǎng)度上設(shè)置了嚴(yán)格的公差。以下是在不同類(lèi)型的系統(tǒng)中應(yīng)用PCB跡線長(zhǎng)度匹配的一些極佳實(shí)踐。

什么是走線長(zhǎng)度匹配?

PCB走線長(zhǎng)度匹配恰如其名:在兩條或多條PCB走線在板上布線時(shí),您要匹配它們的長(zhǎng)度。這些跟蹤可能是以下之一:

并行路由的多條單端走線

差分對(duì)的每一端

多個(gè)并聯(lián)的差分對(duì),單端或差分對(duì)與時(shí)鐘信號(hào)并行布線

數(shù)字信號(hào)的PCB走線不需要完全匹配長(zhǎng)度。在上升沿上總會(huì)有一定的抖動(dòng),因此并行路由的信號(hào)永遠(yuǎn)不可能完美匹配長(zhǎng)度。目的是將長(zhǎng)度或時(shí)序失配減小到某個(gè)極限值以下。允許的長(zhǎng)度不匹配和時(shí)序不匹配與信號(hào)速度有關(guān):

如果您不知道系統(tǒng)中允許的走線長(zhǎng)度不匹配,請(qǐng)不要擔(dān)心。只需檢查您的信令標(biāo)準(zhǔn),接口標(biāo)準(zhǔn)或組件數(shù)據(jù)表即可。由于計(jì)算機(jī)外圍設(shè)備的標(biāo)準(zhǔn)化程度很高,因此大多數(shù)組件都使用許多高速信令標(biāo)準(zhǔn)之一,并且您可以在規(guī)格中輕松找到路由規(guī)格,所需的阻抗和允許的長(zhǎng)度不匹配。

長(zhǎng)度不匹配也可以使用信號(hào)速度轉(zhuǎn)換為定時(shí)不匹配,盡管在選擇數(shù)字信號(hào)的速度時(shí)要格外小心。這是因?yàn)橥ǔR孕∮?/span>1 ns的邊沿速率運(yùn)行的現(xiàn)代數(shù)字信號(hào)將具有高達(dá)GHz的帶寬,并且只能容忍非常小的失配。PCB基板中的分散會(huì)導(dǎo)致信號(hào)速度隨頻率變化。例如,FR4在?1 GHz以下具有正常色散,因此較低的頻率比較高的頻率更早到達(dá)接收器。

跡線長(zhǎng)度匹配的目標(biāo)是防止并行數(shù)據(jù)總線上的時(shí)滯。偏斜只是指兩個(gè)或多個(gè)數(shù)字信號(hào)的上升沿之間的時(shí)序不匹配。在并行總線中,在最短走線上傳播的信號(hào)將最早到達(dá),因此它將在總線上的其他信號(hào)之前觸發(fā)下游門(mén)。行業(yè)標(biāo)準(zhǔn)的PCB設(shè)計(jì)軟件將允許您在原理圖中定義總線和差分對(duì),但您需要在布局中強(qiáng)制使用跡線長(zhǎng)度匹配,以使偏斜度在允許的范圍內(nèi)。

偏斜和走線長(zhǎng)度匹配

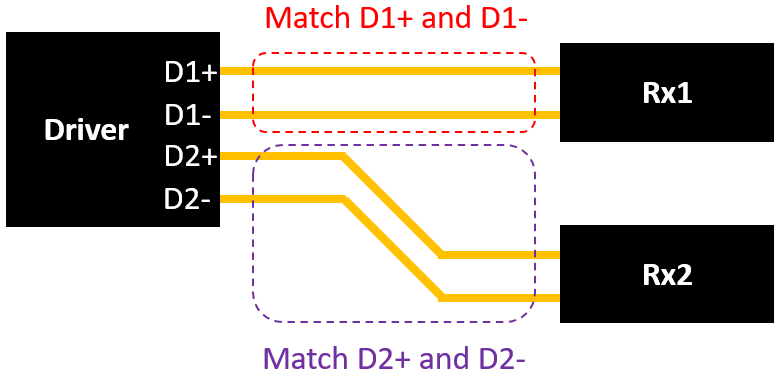

多個(gè)單端網(wǎng)絡(luò)中的長(zhǎng)度匹配非常簡(jiǎn)單;只需添加調(diào)整結(jié)構(gòu),以確保總線上的所有走線都具有相同的長(zhǎng)度。調(diào)整結(jié)構(gòu)將在下面更詳細(xì)地討論。對(duì)于差分對(duì),單個(gè)差分對(duì)的每一端應(yīng)長(zhǎng)度匹配。下圖顯示了將PCB跡線長(zhǎng)度匹配應(yīng)用于差分對(duì)的示例。

上面顯示的差分對(duì)在單個(gè)驅(qū)動(dòng)器(例如,FPGA)和兩個(gè)不同的接收器之間路由。每個(gè)接收器分別讀取D1和D2上的差分信號(hào)。在此,差分對(duì)D1的每一端都需要進(jìn)行長(zhǎng)度匹配。類(lèi)似地,差分對(duì)D2的每一端都需要長(zhǎng)度匹配。但是, D1和D2不需要彼此匹配,因?yàn)樗鼈儧](méi)有并行傳輸數(shù)據(jù)。這些差分對(duì)中的每對(duì)一次只傳送一個(gè)比特,我們只需要進(jìn)行長(zhǎng)度匹配以確保在每對(duì)中消除共模噪聲。

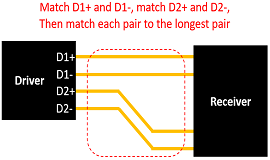

如果您有多個(gè)差分對(duì)攜帶并行數(shù)據(jù),則每個(gè)差分對(duì)都需要匹配,然后這些對(duì)必須彼此匹配。如下所示,其中單個(gè)驅(qū)動(dòng)程序正在將并行數(shù)據(jù)發(fā)送到單個(gè)接收器。這樣可確保每個(gè)差分對(duì)都能充分消除共模噪聲,并確保接收并行數(shù)據(jù)而不會(huì)出現(xiàn)位之間的偏差。

時(shí)鐘信號(hào)

下一個(gè)自然要問(wèn)的問(wèn)題與時(shí)鐘信號(hào)有關(guān):來(lái)自系統(tǒng)時(shí)鐘的信號(hào)應(yīng)如何在具有多個(gè)鏈IC的整個(gè)數(shù)字系統(tǒng)中進(jìn)行長(zhǎng)度匹配?在上面的示例中,時(shí)鐘信號(hào)需要來(lái)自某個(gè)地方,以便接收器鎖存。答案是:在此拓?fù)渲胁皇褂孟到y(tǒng)時(shí)鐘信號(hào)!

在大型數(shù)字系統(tǒng)中,使用系統(tǒng)時(shí)鐘來(lái)觸發(fā)組件鏈中的每個(gè)IC極為困難。這是因?yàn)槊總€(gè)IC可能具有不同的邏輯門(mén)延遲,上升時(shí)間和總體信令標(biāo)準(zhǔn)。因此,現(xiàn)代數(shù)字組件使用源同步時(shí)鐘或嵌入式時(shí)鐘。在前者中,時(shí)鐘信號(hào)與并行數(shù)據(jù)跡線一起在一條跡線中路由,并且該時(shí)鐘跡線需要與其他數(shù)據(jù)跡線長(zhǎng)度匹配。

在嵌入式時(shí)鐘的情況下,沒(méi)有時(shí)鐘跟蹤。嵌入式時(shí)鐘用于串行通信(例如,SerDes通道),而時(shí)鐘信號(hào)被編碼為串行數(shù)據(jù)流中的前幾個(gè)位。如果您要設(shè)計(jì)帶有差分對(duì)(例如LVDS)的SerDes通道,則仍需要使用上述技術(shù)對(duì)差分對(duì)進(jìn)行長(zhǎng)度匹配。

長(zhǎng)度調(diào)整結(jié)構(gòu)

存在三種常見(jiàn)的PCB走線長(zhǎng)度調(diào)整結(jié)構(gòu),每種結(jié)構(gòu)都可以在其自己的文章中進(jìn)行討論。這些結(jié)構(gòu)的其他一些名稱(chēng)是切回路由和蛇形路由。這些不同的結(jié)構(gòu)中的每一個(gè)都會(huì)對(duì)傳輸線阻抗和FEXT產(chǎn)生一些有趣的影響

如果您要對(duì)匹配的差分對(duì)組進(jìn)行長(zhǎng)度匹配,那么每一個(gè)都是延長(zhǎng)差分對(duì)的好選擇。無(wú)論本結(jié)構(gòu)如何應(yīng)用,都應(yīng)嘗試使長(zhǎng)度調(diào)整部分保持對(duì)稱(chēng),如果結(jié)構(gòu)缺乏對(duì)稱(chēng)性,共模噪聲仍將被充分消除。

當(dāng)逃避過(guò)孔或長(zhǎng)度不匹配很短時(shí),應(yīng)嘗試將這些結(jié)構(gòu)之一應(yīng)用于網(wǎng)絡(luò)的源端,而不是接收器端。如果在接收器端應(yīng)用該結(jié)構(gòu),則可能無(wú)法充分消除軌跡中較早接收到的任何共模噪聲。對(duì)于過(guò)孔附近的短失配,可以在源端施加一個(gè)小的延遲(稱(chēng)為相位匹配)。

模擬差分信號(hào)呢?

上面討論的思想適用于數(shù)字信號(hào),但是模擬信號(hào)也可以作為差分對(duì)進(jìn)行路由。即使在非常高的頻率下,這在許多系統(tǒng)中也很少見(jiàn)。但是,可以使用差分運(yùn)算放大器將模擬信號(hào)作為差分對(duì)進(jìn)行路由。像德州儀器(TI)這樣的公司提供高帶寬(?GHz帶寬)差分運(yùn)算放大器組件,非常適合路由模擬差分對(duì)。使用這些組件,您可以輕松地將模擬信號(hào)路由到電路板上,并且當(dāng)需要與單端模擬IC接口時(shí),可以轉(zhuǎn)換回單端模擬信號(hào)。

模擬差分信號(hào)需要精確的長(zhǎng)度匹配,就像數(shù)字差分信號(hào)一樣。區(qū)別在于模擬差分信號(hào)類(lèi)似于三相AC布線,其中相鄰的模擬接地層用作該對(duì)兩端的參考。盡管數(shù)字信號(hào)顯然不需要接地層,但出于上述原因,將接地層放置在數(shù)字差分對(duì)附近是有利的。

上面顯示的PCB跡線長(zhǎng)度匹配準(zhǔn)則也需要與模擬差分對(duì)一起使用,因?yàn)樗鼈儠?huì)累積偏斜,就像差分信號(hào)一樣。它們還需要非常精確的相位匹配,并且容易受到相位噪聲的影響。用于最小化抖動(dòng)的相同PDN設(shè)計(jì)要點(diǎn)也適用于防止相位噪聲的模擬組件。但是,幸運(yùn)的是,在設(shè)計(jì)模擬PDN時(shí),您正在以較小的帶寬工作,這使得將模擬PDN阻抗最小化變得容易得多。